2025/12/07 12:03

Z2 – Lithographically fabricated IC in a garage fab

RSS: https://news.ycombinator.com/rss

要約▶

Japanese Translation:

著者は、DIYで低コストのポリシリコンゲートプロセスを用いてIntelの最初のプロセッサ技術を模倣し、2.4 mm² のダイに10×10配列(合計100トランジスタ)を製造しました。以前のZ1テストチップ(6トランジスタ)に続き、新しいZ2チップは完全な電気特性評価が可能です:Vth ≈ 1.1 V、Cgs < 0.9 pF、立ち上がり/落下時間 < 10 ns、オン/オフ比 ≈ 4.3 × 10⁶、漏れ電流 932 pA(Vds = 2.5 V)(環境光下では約100倍高い)。これらの数値は、2.5–3.3 V のロジックレベルで信頼性ある動作を示しています。

製造は自己整列型「ゲートファースト」プロセスであり、イオン注入を省略し、水・アルコール・アセトン・リン酸・フォトレジスト・デベロッパー・N‑タイプドーパント・HF/CF₄/CHF₃ RIE・HNO₃ などの一般的な実験室化学物質のみを使用し、クリーンルームは不要です。約10 nm のSiO₂ゲート酸化膜と300 nm のポリシリコンを有する25 × 200 mm ウェーハを約45ドルで購入しました。製造には15チップ(1,500トランジスタ)が関与し、少なくとも1チップは完全に機能し、2チップが「ほぼ機能」しているため、推定トランジスタ歩留まりは80 %です。最も頻繁な欠陥はソース/ドレインがバルクシリコンと短絡していることです。

今後の作業にはテスト自動化、歩留まり向上、およびオペアンプやメモリアレイなどより複雑なデジタル/アナログ回路への技術拡張が含まれます。成功すれば、このDIY手法はホビイストや小規模ラボの参入障壁を低減し、ニッチなイノベーションを促進し、少量プロトタイプ用に商業製造所への依存度を削減する可能性があります。

本文

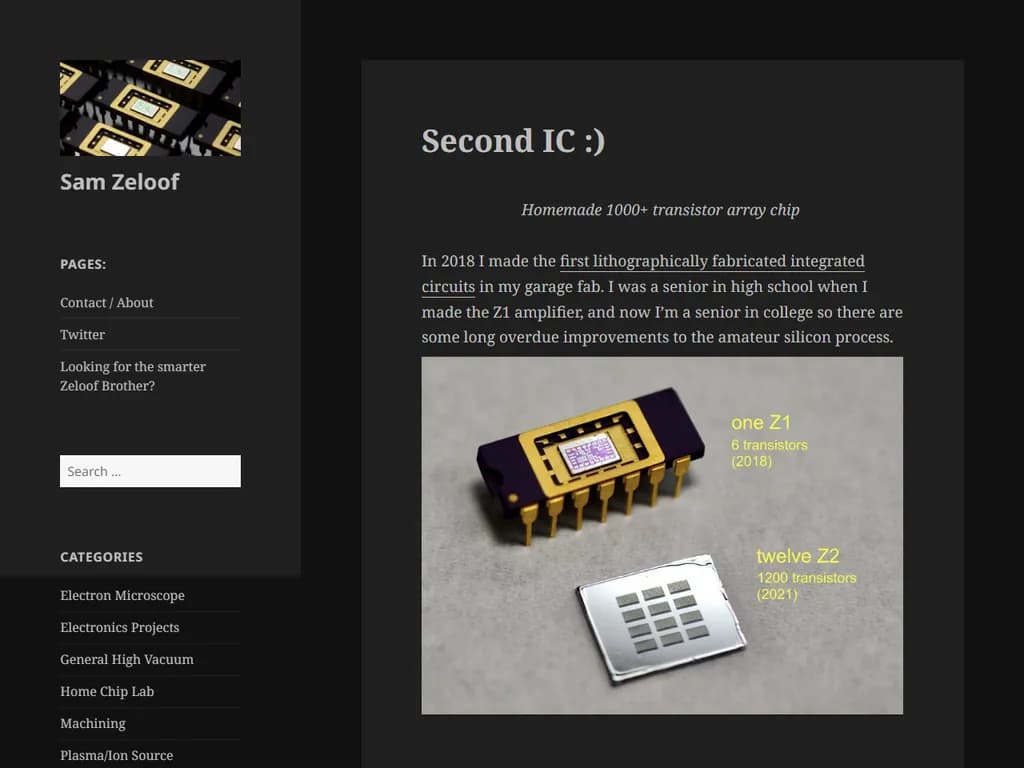

自作 1000 個以上のトランジスタ配列チップ

2018 年に、私はガレージでファブを設置し、最初のリソグラフィー製造された集積回路を実装しました。

高校4年生だった頃に Z1 アンプを構築したときはまだ初心者でしたが、現在は大学院卒業を目前に控えつつ、アマチュア向けシリコンプロセスの改善に取り組んでいます。

- Z1 – 6 個のトランジスタ。プロセスや装置開発用として優れたテストチップです。

- Z2 – 10 µm ポリシリコンゲートプロセス(Intel の最初のプロセッサと同じ技術)で 100 個のトランジスタを搭載。

- 最新のチップは、プロセスをテスト・特性評価し調整するための単純な 10 × 10 配列です。これはより高度な DIY コンピュータチップへ進む上で重要なステップです。

- Intel 4004:2 200 トランジスタ

- 私のチップ(同一シリコン):1 200 トランジスタ

パフォーマンス改善

以前はメタルゲートプロセスを使用していました。アルミニウムゲートと基板シリコンとの間に大きなワークファンクション差が生じ、しばしば高い閾値電圧(>10 V)になっていました。そのトランジスタは、9 V バッテリーを必要とするギター・ディストーションペダルやリングオシレーター LED ブリンクなどのプロジェクトで使用されていました。

ポリシリコンゲートに切り替えることで以下のような特性が得られました:

| パラメータ | 値 |

|---|---|

| Vth | 1.1 V |

| VGS,max | 8 V |

| Cgs | <0.9 pF |

| 立ち上がり/立ち下がり時間 | <10 ns |

| オン/オフ比 | 4.3 × 10⁶ |

| リーク電流(VDS=2.5 V) | 932 pA |

リーク電流は室内照明下で約 100 倍に増加します。

特性データ

- 1 MHz で 50 Ω ロード

- 20 MHz で 50 Ω ロード

(図は省略)

チップレイアウト & プロービング

ダイ面積は約 2.4 mm²(以前の IC の ¼)と小さく、プローブが難しくなります。

10 × 10 配列の N‑チャネル FET は次のように共有します:

- カラム – 共通ゲート接続

- ロー – シリーズ接続で共通ソース/ドレイン端子

この設計により、メタルパッドが十分大きく保たれ、各 FET が数個の極小パッドしか持たない問題を回避しています。

(プローブ映像へのリンクは省略)

単一の 10 µm NMOS トランジスタでは、金属層にわずかな不整合が見られます(左側接触部の一部が露出)。赤枠でポリ結晶シリコンを示し、青はソース/ドレインです。

プロセス概要

- ウェーハ購入 – 10 nm の薄い SiO₂ と 300 nm の厚いポリシリコン。

- 25 × 200 mm ウェーハ(eBay で約 $45)なら生涯分足ります。

- アクティブエリアをエッチ

- ソース/ドレインにドーピング

- ポリゲートをエッチ

- 絶縁層の堆積(フォトレジストをハードベークしたフィールド絶縁体として使用)

- 接触部をエッチ

- 金属を堆積

- 金属をエッチ

(図は省略)

ウェーハにゲート酸化膜とポリシリコンがすでに存在するため、従来のフィールドオキサイドを成長させることはポリ層を破壊します。修正プロセスではポリシリコン自体をドーピングマスクとして使用し、ハードベークしたフォトレジストをフィールド絶縁体にしてステップ構造(横断面でオレンジ領域)を作ります。

ゲート長測定 – 理想的には 1 µm SiO₂ (CVD) を使用しますが、ここでは約 250 °C のハードベークフォトレジストが簡易代替として機能しています。SiO₂ エッチはバッファド HF または RIE で行います。

現状と展望

- 15 枚のチップを製造(1 500 トランジスタ)。

- 少なくとも 1 枚は完全に動作し、少なくとも 2 枚は「ほぼ動作」(約 80 % の歩留まり)しています。

- 最も頻繁な欠陥:ドレイン/ソースがバルクシリコンチャネルに短絡。

- 今後のステップ:テストを自動化し、FET 特性の統計データを収集し、より複雑なデジタル/アナログ回路を設計。

巨大な合成ダイ画像は省略

私の作業をご覧いただきありがとうございます。ご意見や質問があればお気軽にお問い合わせください!